邊沿觸發(fā)器與計數(shù)器 計算機時序邏輯的基石

在探索計算機軟硬件背后隱秘語言的過程中,我們抵達了一個構(gòu)建現(xiàn)代數(shù)字系統(tǒng)心臟的關鍵節(jié)點:時序邏輯電路。第14章將焦點對準了兩種基礎而強大的元件——邊沿觸發(fā)器和由它們構(gòu)成的計數(shù)器,它們共同為計算機的“節(jié)奏”與“記憶”奠定了基礎。

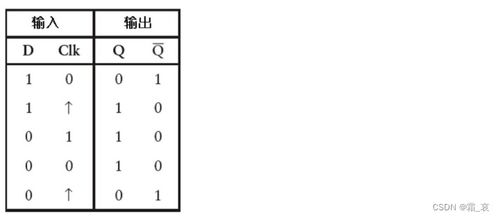

邊沿觸發(fā)器是數(shù)字電路中的一種基本存儲單元,其核心特性在于僅在時鐘信號的特定跳變時刻(上升沿或下降沿)捕獲并鎖存輸入數(shù)據(jù)的狀態(tài),而非在整個時鐘電平期間都響應。這種邊沿觸發(fā)的機制,對比于早期簡單的電平觸發(fā)鎖存器,提供了更高的抗干擾能力和可靠性。當時鐘邊沿到來時,觸發(fā)器采樣此時的輸入值(如D觸發(fā)器的D端),并將該值保持到輸出端,直至下一個有效時鐘邊沿。這一特性使得電路行為在時間上被精確離散化,確保了即使在有噪聲或路徑延遲存在的復雜系統(tǒng)中,數(shù)據(jù)也能在確定的時刻被穩(wěn)定存儲和傳遞,這是實現(xiàn)同步數(shù)字系統(tǒng)的前提。

將邊沿觸發(fā)器作為構(gòu)建模塊,我們可以創(chuàng)造出功能豐富的時序電路,其中計數(shù)器是最典型和廣泛應用的代表之一。計數(shù)器本質(zhì)上是一組相互連接的觸發(fā)器,其狀態(tài)按照預定的序列(通常是二進制序列)隨每個時鐘脈沖而規(guī)律變化。例如,一個由4個D觸發(fā)器構(gòu)成的4位二進制異步計數(shù)器,每個觸發(fā)器的輸出作為下一個觸發(fā)器的時鐘信號,從而實現(xiàn)從0000到1111的循環(huán)計數(shù)。更復雜、速度更快的同步計數(shù)器,則將所有觸發(fā)器的時鐘端連接在一起,通過組合邏輯來控制次態(tài),實現(xiàn)精確的同步翻轉(zhuǎn)。

在計算機的軟硬件層面,計數(shù)器的作用無處不在且至關重要:

- 硬件層面:計數(shù)器是CPU中程序計數(shù)器(PC)的核心物理實現(xiàn)。程序計數(shù)器保存著下一條待執(zhí)行指令的內(nèi)存地址,每完成一條指令的取指,它就自動加1(或根據(jù)跳轉(zhuǎn)指令被置入新值),從而驅(qū)動指令執(zhí)行的順序流。計數(shù)器還用于生成定時信號、分頻、測量時間間隔、控制存儲器地址序列等,是協(xié)調(diào)硬件各部件時序運作的節(jié)拍器。

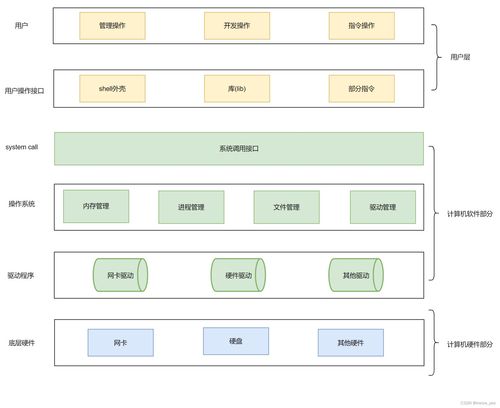

- 軟件與系統(tǒng)層面:軟件程序員雖不直接操縱觸發(fā)器,但程序的行為完全依賴于底層計數(shù)器創(chuàng)造的時序環(huán)境。操作系統(tǒng)的時間片輪轉(zhuǎn)調(diào)度、定時器中斷、性能計數(shù)器的讀取,乃至高級編程語言中的循環(huán)控制變量,其本質(zhì)都映射到底層硬件計數(shù)器的遞增與比較操作。計數(shù)器定義了計算機對時間流逝和事件次序的量化感知。

因此,邊沿觸發(fā)器提供了數(shù)字記憶的“原子”,而計數(shù)器則將這些原子組織成能夠“計數(shù)時間”與“序列狀態(tài)”的有機體。它們共同隱匿在芯片的深處,將連續(xù)的物理時間轉(zhuǎn)化為離散的邏輯步驟,使得計算機能夠一步一步、有條不紊地執(zhí)行軟件指令,從最底層的硬件振蕩到最上層的軟件運行,構(gòu)成了計算過程可靠進行的時序骨架。理解它們,就理解了計算機如何從一個瞬間到下一個瞬間,有序地創(chuàng)造奇跡。

如若轉(zhuǎn)載,請注明出處:http://www.bsdgjm.com/product/61.html

更新時間:2026-03-01 11:08:12